International Journal of Computer Science and Engineering (IJCSE) ISSN (P): 2278–9960; ISSN (E): 2278–9979 Vol. 13, Issue 2, Jul–Dec 2024; 35–54 © IASET

# PERFORMANCE ANALYSIS OF CACHE MEMORY DESIGN FOR SINGLE BIT ARCHITECTURE FOR ULTRA-LOW POWER

Varun Dixit<sup>1</sup> & Apoorva Mishra<sup>2</sup>

<sup>1</sup>Senior Member of Technical Staff at Omnissa LlC, <sup>2</sup>Independent Researcher

#### **ABSTRACT**

In this paper, the design analysis of ultra-low-power cache memory design for single-bit architecture has been proposed and implemented. Cache Memory Design for Single Bit Architecture is composed of a circuit of the write driver circuit, six transistors static random access memory cell, and different types of sense amplifiers such as voltage differential sense amplifier, current differential sense amplifier, and charge transfer differential sense amplifier. Power reduction techniques are also applied over different blocks of architecture, such as sense amplifiers and six transistors static random access memory cells. The performance of different architectures has been analyzed in terms of power consumption, the number of transistors, and delay in sensing. The results depicted that single-bit six transistor static random access memory cell voltage mode differential sense amplifier architecture consumes 13.16µW of power, 12.5ηs delay in sensing, with 30 transistors compared to others. Furthermore, Process Corner Simulation and Monte Carlo Simulation also have been done to check the robustness of the circuit. The conclusion depicts that single bit six transistor static random access memory cell with power reduction sleep transistor technique voltage mode differential sense amplifier with power reduction sleep transistor technique in architecture consume 8.988 µW of power with 34 number transistors and lowest chip area 62.613 × 30.48 mm2.

KEYWORDS: Six Transistor Static Random-Access Memory (6T-SRAM), Cache Memory Design for Single Bit Architecture (CMDSBA), Single Bit Six Transistor Static Random-Access Memory Current Differential Sense Amplifier Architecture (SB6TSRAMCDSAA), Single Bit Six Transistor Static Random Access Memory Charge Transfer Differential Sense Amplifier (SB6TSRAMCTDSAA), Single Bit Six Transistor Static Random Access Memory Voltage Differential Sense Amplifier (SB6TSRAMVDSAA).

Article History

Received: 20 Aug 2024 | Revised: 02 Sep 2024 | Accepted: 04 Sep 2024

# 1. INTRODUCTION

6T-SRAM is frequently used in microprocessors and on-chip system memory. 6T-SRAMs are utilized in a system-on-chip to store big caches on CPU cores and IPs such as graphics, audio, video, and image processing systems. 6T-SRAMs are used in high-performance graphics and microprocessors. 6 T-SRAMs, on the other hand, are utilized in processors for mobile, portable, and consumer devices, requiring comparatively minimal power. As 6T-SRAMs are used as large storage

systems on these devices, it is vital to maximizing their density. In some situations, up to 1024 6T-SRAM-bit cells are typically linked to the same bitlines to achieve the maximum density and array efficiency. Display sensor amplifiers are necessary for speed due to the high availability of the bit lines. Sensory amplifiers can read the data instead of waiting for the entire rail-to-rail swing by sensing a small differential voltage swing on the bit lines. A minimum amount of differential voltage on bit lines for reliability is required for conventional voltage sensing amplifiers. The time it takes for this differential voltage to be generated is based on bit capacity. The amount of dynamic power needed to precharge the bit lines is increased in direct relation to the required differential voltage. Because of the lower mobile and embedded CPU power needs, sensor amplifiers with less power than classic voltage differential sense amplifiermethods are needed. This paper compares the Single Bit Six Transistor Static Random-Access Memory Current Differential Sense Amplifier, and Single Bit Six Transistor Static Random Access Memory Charge Transfer Differential Sense Amplifier, and Single Bit Six Transistor Static Random Access Memory Voltage Differential Sense Amplifier. CMDSBA has been proposed in the proposed work employing several SAs. Furthermore, power reduction (TPR) techniques such as power reduction dual sleep technique, power reduction forced stack technique, power reduction sleepy stack technique, and power reduction sleep transistor technique have been implemented.

## 1.1 Techniques of Power Reduction

In this section, a small introduction to power reduction techniques is discussed.

# 1.1.1 Power Reduction Dual Sleep Technique (PRDST)

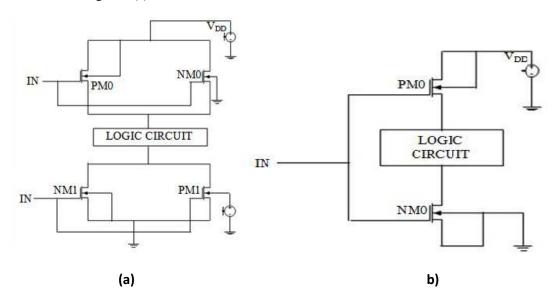

Four transistors are utilized in this technique: PM0, PM1, and two NM0, NM1. In this approach, PM0 and NM0 are linked in parallel instead of the circuitry's voltage supply, while PM1 and NM1 are connected in parallel in the logic circuit in place of the ground [22]. PM0 and NM0 have the same input in this method, whereas PM1 and NM1 have the same information, as shown in Figure:1 (a).

Figure: 1 (a) Power Reduction Dual Sleep Technique (b) Power Reduction Forced Stack Technique

## 1.1.2 Power Reduction Forced Stack Technique (PRFST)

The forced stack approach uses PM0 instead of voltage supply and NM0 instead of ground in the logic circuit, as shown in Figure: 1 (b). Both mos have the same input in this approach. When PM0 is in the active zone, NM0 is in the cut-off region in this approach [19]. As a result, the circuit does not require constant power, resulting in lower power consumption.

## 1.1.3 Power Reduction Sleepy Stack Technique (PRFSST)

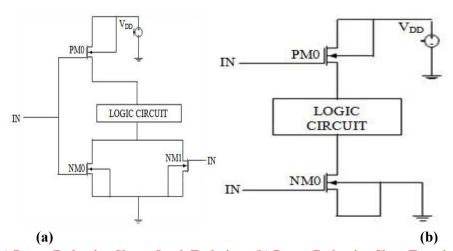

As illustrated in Figure 2, three transistors are utilized in this technique: PM0, NM0, and NM1 (a). Both NM0 and NM1 are linked in parallel in this approach. PM0 is utilized in place of the voltage supply, while NM0 and NM1 are used in place of the ground in the logic circuit [20]. PM0 and NM0 have the same input in this method, but NM1 has a separate input. PM0 is in the active region, NM0 is in the cut-off zone, and NM1 is in the activepart while the circuit is in operating mode. PM0 is in the cut-off area in standby mode, NM0 is in the active region, and NM1 is in the cut-off region [21].

## 1.1.1 Power Reduction SleepTransistor Technique (PRSTT)

Figure 1(a) shows that the sleep transistor technology is also a switching technique. Two transistors, PM0 and NM0, are switches in the sleep transistor method. Instead of a voltage source, PM0 is utilized in this approach, and NM0 is used in the logic circuit instead of the ground. When the logic circuit is in operation, PM0 is in the active area, and NM0 is also in the active region; however, when the circuit is in standby mode, PM0 is in the cut-off region, and NM0 is also in the cut-off region, resulting in a lower power consumption [17, 18].

Figure: 2(a) Power Reduction Sleepy Stack Technique (b) Power Reduction Sleep Transistor Technique

PM0 is in the active region, NM0 is in the cut-off area, NM1 is in the active part, and PM1 is in the cut-off region while the circuit is in operating mode [23]. PM0 is in the cut-off area, NM0 is in the active part, NM1 is in the cut-off region, PM1 is in the active region while the circuit is in standby mode. As demonstrated in Figure: 2 (b) [24], our circuitry uses less power. Apart from the introduction, Section II covers the purpose and history of a single-bit cache memory design andeach Block's circuitry and working mechanism. Section III explained the suggested circuit architecture with output waveforms and comparisons. In Section IV, the conclusion has been described.

<u>www.iaset.us</u> editor@iaset.us

## **Section II**

#### 1. Literature Review

Sense amplifiers must work fast while using the least possible power, depending on the performance and power requirements. The high-bit line capacitance is a significant performance limit. Table:1 describe work done by different authors from 2002 to 2011.

| Year | Author                  | Features                           | Sensing<br>Delay | Supply<br>Voltage |

|------|-------------------------|------------------------------------|------------------|-------------------|

| 2002 | Chrisanthopouloset al.  | Conventional SA                    | 7.1 ns           | 2.5V              |

| 2002 | Chrisanthopoulos et al. | Clamped Bit Line SA                | 0.35 ns          | 2.5V              |

| 2002 | K.S. Yeo et al.         | Low power current SA               | 1.04 ns          | 2.0V              |

| 2002 | Chrisanthopoulos et al. | Simple Four Transistor SA          | 1.85 ns          | 2.5V              |

| 2004 | Chun- lung Hsu et al.   | High-Speed SA                      | 0.51 ns          | 1.8V              |

| 2005 | Z. H. Kong et al.       | Ultra-low power                    | 1.46 ns          | 1.8V              |

| 2007 | Sandeep Patilet al.     | Self-Biased Charge-<br>Transfer SA | 0.723 ns         | 1.8V              |

| 2008 | Ya-Chun Lai et al.      | Latch Type SA                      | 0.33 ns          | 1.8V              |

| 2008 | Anh-Tuan Do et al.      | Fully Current Mode SA              | 0.38 ns          | 1.8V              |

| 2008 | Do Anh-Tuan et al.      | High-Speed SA                      | 0.26ns           | 1.8V              |

| 2011 | Anh-Tuan Do et al.      | Alpha Latch SA                     | 0.566 ns         | 1V                |

| 2011 | Anh-Tuan Do et al.      | Decoupled SA                       | 0.214 (ns)       | 1V                |

Table 1: Work done by different authors from 2002 to 2011

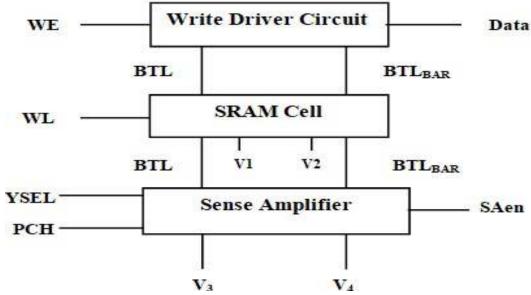

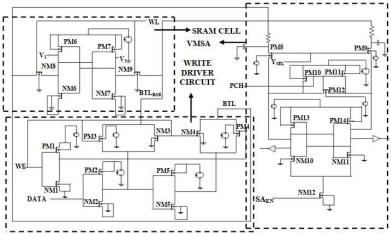

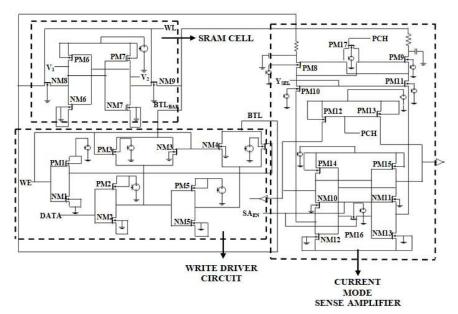

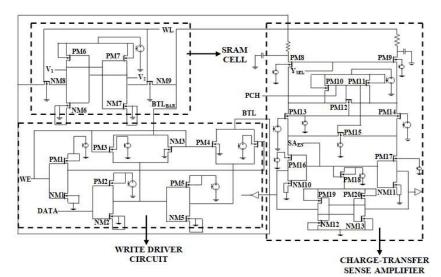

# 2. Cache Memory Design for Single Bit Architecture

The architecture is made up of threeBlockswith three differentialsense amplifier circuits as a circuit of write driver (CWD), 6T-SRAM cell, and sense amplifier (SA), as shown in Figure: 3[25]. It consists of six input pins and five output pins. CWD has two input pins (Word Enables (WE) and Data), two output pins, BTL and BTL<sub>BAR</sub>, 6T-SRAM has a single input pin, a word line (WL), and two output pins,  $V_1$  and  $V_2$ . On the other hand, SA is coupled through bit lines to the 6T-SRAM cell. SA has three YSEL input pins,  $P_{CH}$  (precharge) and Sense amplifier (SA<sub>EN</sub>), and two output pins ( $V_3$  and  $V_4$ ).

Figure 3: Block Diagram of Cache Memory Design for Single Bit Architecture

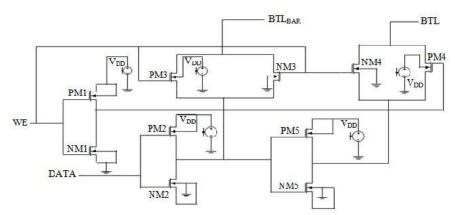

## 3.1 Circuit of Write Driver

In the 6T-SRAM cell, the CWD is utilized to save data. Figure: 4 shows a CWD scheme. CWD lowers the writing margin. The circuit has the task of loading or unloading the bit lines of the memory cell. Including PM1, PM2, PM3, PM4, PM5, NM1, NM2, NM3, NM4, and NM5, ten transistors include in a circuit. It consists of two WE and Data inputs and two BTL and BTL<sub>BAR</sub> output pins linked to the 6T-SRAM cell input transistors.

Figure: 4 Circuit of Write Driver Schematic.

## 3.2 6T-SRAMCell Schematic

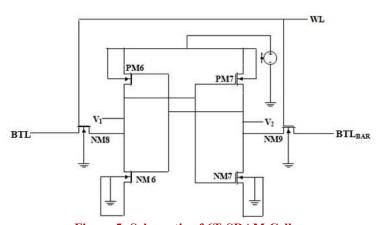

In computers, 6T-SRAM is utilized as cache memory. It has a six-transistor configuration. As illustrated in Figure 5 [29], it has bistable (cross-coupled) inverters for storage (PM6, PM7, NM6, and NM7 function as crossed coupled inverters). The NM8 and NM9 access transistors are linked to BTL and  $BTL_{BAR}$  and are used to access stored data for reading and writing operations.

Figure 5: Schematic of 6T-SRAM Cell.

WL control access; when WL= low hold operation, so access transistors are off, data held in latch and when WL= high, read or write operation has been done, access transistors are turned ON,a voltage applied to BTL and BTL<sub>BAR</sub>, data in latch overwritten with new value and BTL and BTL<sub>BAR</sub> are read by SA's [30]. It is connected to the CWD and SA through BTL and BTL<sub>BAR</sub>. When connected to the SA, resistance and capacitance are connected in parallel through BTLs [31].Memory cell transistor size affects 6T-SRAM performance and reliability. The architecture adopted for a cell should obey two basic rules for the proper functioning of 6T-SRAM.

NM6 and NM7 pull-down network transistors must be approximately equal to or more potent than the access transistors (NM8 and NM9). This rule ensures read operation stability.

The pull-up network transistors in PM6 and PM7 should be equal to or less than the access transistor (NM8 and NM9). This rule ensures that the value in the Bit-Cell is swapped during the writing process.

# 3.2 Sense Amplifier's

The SA is an important circuit in 6T-SRAM architecture. SA is used for a read operation in the 6T-SRAM cell. During reading operation BTL= low and BTL<sub>BAR</sub>= high or BTL= high and BTL<sub>BAR</sub>= low. This slow discharge of the bit cells BTL's capacitance and access transistor is small. Due to this, a small difference between bit lines is sensed and amplified by SA. The total width of the transistorshas been kept equal for all SAs. In this paper, three different types of amplifiers are used such as:

- ➤ Voltage Differential Sense Amplifier

- > Current Differential Sense Amplifier

- ➤ Charge-Transfer Differential Sense Amplifier

## **SECTION III**

## 4. Analysis of Result

Figure 6 Depicts a Single-Bit 6T-SRAM VDSA Architecture [25] Using CWD, a 6T-SRAM Cell, and VDSA as the SA.

Figure 6: Schematic of Single Bit 6T-SRAM VDSA Architecture.

The BTLs and the SA output are both Pch high during the precharge period.  $Y_{SEL}$ = high, PCH= low, PM8, and PM9 are in the cut-off mode, while PM10, PM11, and PM12 are in active mode, and it Pch the BTL to the full rail swing, WL= low (no read operation), and  $SA_{EN}$ = low (no data sensed) since NM12 is in cut-off mode.

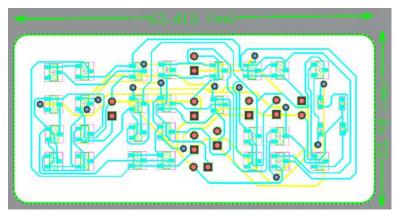

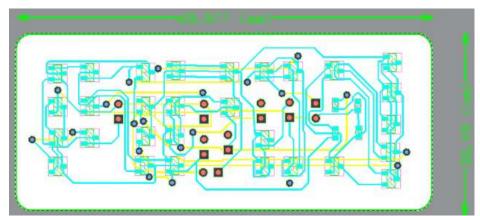

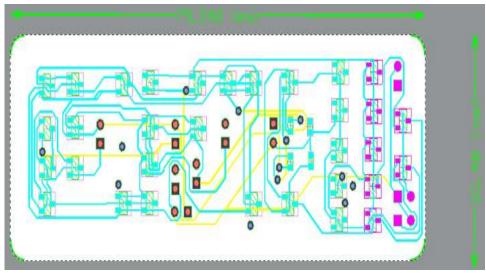

Figure 7: Single Bit 6T-SRAM VDSAArchitecture Chip Design.

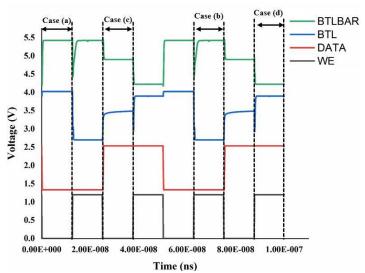

Figure: 7 shows Single Bit 6T-SRAM VDSA Architecture Chip Design. Figure: 8 shows the output waveform of CWD, where WE and DATA are inputs, and BTL and BTL<sub>BAR</sub> are output in four cases. Here, H is denoted High, and L denotes Low.

Figure 8: Circuit of Write Driver Output Waveform.

CASE 1: When WE = L and Data = L,  $BTL_{BAR}$  = H and BTL = H. PM1, PM2, and PM3 are in active mode while PM4 and PM5 are in cut-off mode NM1, NM2, NM3, NM4 are in cut-off mode while NM5 is in active mode.

CASE 2: When WE= H and Data = L, BTLBAR = H and BTL= L. PM2 and PM4 are in active mode while PM1, PM3, and PM5 are in cut-off NM1, NM3, NM4, NM5 are in cut-off mode while NM2 is in active mode.

CASE 3: When WE = L and Data = H, then  $BTL_{BAR} = H/2$  and BTL = H/2. PM1, PM3, and PM5 are in active mode, while PM2 and PM4 are in the cut-off mode, NM2 is in active mode, and NM1, NM3, NM4, and NM5 are in cut-off mode.

CASE 4: When WE = H and Data = H, BTL<sub>BAR</sub> = Land BTL = H. PM4 and PM5 are in active mode while PM1, PM2, and PM3 are cut-off, respectively, NM1, NM2, NM3, NM4 are in active mode while NM5 is in cut-off mode.

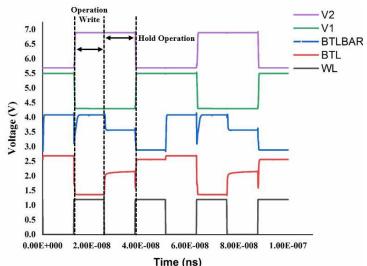

Figure 9: 6T-SRAM Cell Output Waveform.

The output waveform of the 6T-SRAM cell after both the write and hold operations have been held is shown in Figure: 9. The network (PM6 and PM7), pull-down network (NM6 and NM7), and access transistor (NM8 and NM9) all allow data to be stored and read by SA.

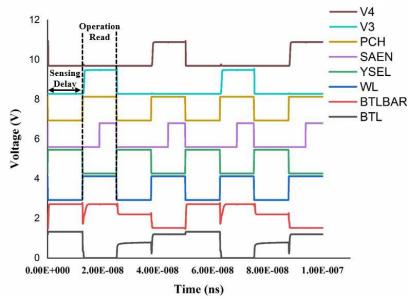

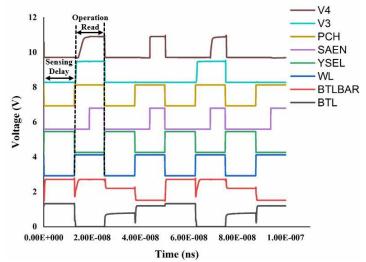

Figure:10 shows the Single Bit 6T-SRAM CDSA Architecture output waveform. During the evaluation phase:  $Y_{SEL} = low$ , Precharge circuits keep high to precharge the bit-lines (i.e.,  $P_{ch} = high$ ), PM8 and PM9 are in active mode, and data on the BTLs pass through while PM10, PM11, and PM12 are in the cut-off mode, WL of 6T-SRAM cell keeps high (i.e., WL = high) for reading operation, i.e., access transistors are turned ON, BTL= low and BTL<sub>BAR</sub> = high, i.e., a voltage difference is high at the output (i.e., at  $V_3$  and  $V_4$ ),  $SA_{EN} = high$  for half positive cycle of WL at this time SA sense the difference between BTL and BTL<sub>BAR</sub> and the stored data has been sensed as because NM12 is in active mode

Figure 10: shows Single Bit 6T-SRAM VDSA Architecture Output Waveform

Figure 11: Single Bit 6T-SRAM CDSA Architecture Schematic.

Figure: 11 shows single-bit 6T-SRAM CDSA architecture composed of CWD, 6T-SRAMC, and VDSA. The description is divided into three different parts: a) the CWD with two input pins (word enable (WE) and bit) and two output pins (BTL and BTL<sub>BAR</sub>), and b) the 6T-SRAM, which is attached to the CWD via bit lines (i.e., BTL and BTL<sub>BAR</sub>), and an input pin (word line (WL) and two output pins ( $V_1$  and  $V_2$ ) and connected through bit lines having capacitance and resistance as a connector between them, c) CDSA which has five input pins ( $Y_{sel}$ , BTL, BTL<sub>BAR</sub>,PCH, and SA<sub>EN</sub>) and two output pins ( $V_3$  and  $V_4$ ).

Figure 12: Single Bit 6T-SRAM CDSA Architecture Chip Design.

Figure:12 shows Single Bit 6T-SRAM CDSA Architecture Chip Design. Figure:13 shows the Single Bit 6T-SRAM CDSA Architecture output waveform, In the precharge phase: the bitlines and the output nodes  $SA_1$  and  $SA_2$  are  $P_{ch}$  high.  $Y_{sel}=V_{DD}$ ,  $P_{ch}=0V$ , PM8and PM9 are in active mode due to while PM10 and PM11are in a cut-off way, due to which data at bit lines in the form of current is stopped at nodes  $SA_1$  and  $SA_2$  and this charge the bit lines, and this causes nodes  $SA_3$  and  $SA_4$  to be pre-discharged to ground as because PM12 and PM13 are in active mode, WL=0V,i.e., no read operation and  $SA_{EN}=0V$ ,i.e., SA does not sense any data as because NM10 and NM11 are in cut-off mode while PM16 is in active mode.

During the evaluation phase, Y<sub>SEL</sub>=0, Precharge circuits keep high to precharge the BTLs (i.e., P<sub>ch</sub>=V<sub>DD</sub>), PM8

and PM9 are in the cut-off mode. The current on the bit-lines is passed through PM10, PM11 which is stored at nodes  $SA_1$  and  $SA_2$  as transistors are in active mode, while PM12 and PM13 are in a cut-off way, and the current is transferred to the nodes  $SA_3$  and  $SA_4$  through the drain of  $P_{mos}$  (PM10 and PM11), WL of 6T-SRAM cell keeps high(i.e., WL=V<sub>DD</sub>) for reading operation, i.e., access transistors are turned ON, BTL= 0V and BTL<sub>BAR</sub>=V<sub>D</sub>),  $SA_{EN}=V_{DD}$  (for half positive cycle of WL) at this time SA sense the difference between BTL and BTL<sub>BAR</sub> and the stored data has been sensed as NM10 and NM11 are in active mode while PM16 is in cut-off mode due to which bias current flow through BTL and BTL<sub>BAR</sub> of sense amplifier while PM16 keep the output equalized.

Figure 13: Shows Single Bit 6T-SRAM CDSA Architecture Output Waveform.

Figure 14: Shows a Single-bit 6T-SRAM CTDSA Architecture having CWD, 6T-SRAM cell, and CTDSA as a Sense Amplifier; the Working of this Circuit is the Same as Single Bit 6T-SRAMVDSA Architecture and Single-Bit 6T-SRAMCDSA Architecture.

Figure: 14 Single Bit 6T-SRAM CTDSA Architecture Schematic.

The circuit is divided into two parts. In the first part, the common-gate cascade comprised PM13, PM16, and NM10 (and PM14, PM17 and NM12). The  $P_{mos}$  (PM13 and PM14) are biased at potential  $V_b$ . The second part, PM18,

PM19, PM20, NM12and NM13made cross-coupled inverters, latches the output of the common-gate amplifier ( $SA_1$  and  $SA_2$ ). In the precharge phase: the bit lines and all the internal nodes ( $SA_1$ ,  $SA_2$ ,  $SA_3$ , and  $SA_4$ ) are pre-charged.  $Y_{SEL}=V_{DD}$ ,  $P_{ch}=0V$ , PM8, and PM9 are in cut-off mode while PM10, PM11, and PM12 are in a playfulway, which precharge the bit lines to the  $V_{DD}$ , WL=0V,i.e., no read operation and  $SA_{EN}=V_{DD}$ ,i.e., PM16, PM17, and PM18 are in cut-off mode while NM10 and NM11 is an active mode which precharge the bit lines at internal nodes at  $SA_5$  and  $SA_6$ . During the evaluation phase:  $Y_{scl}=0$ , precharge circuits keep high to precharge the bit lines (i.e.,  $P_{ch}=V_{DD}$ ), PM8, andPM9 are in active mode. Data on the bitlines are passed from 6T-SRAM to SA at nodes  $SA_1$  and  $SA_2$ . While PM10, PM11, and PM12 are in the cut-off mode, WL of the 6T-SRAM Cell keeps high (i.e.,  $WL=V_{DD}$ ) for reading operation, i.e., access transistors are turned ON, BTL= 0V, and BTL<sub>BAR</sub>= $V_{DD}$ , i.e.,a voltage difference is  $V_{DD}$  at the output (i.e., at  $V_3$  and  $V_4$ ),  $SA_{EN}=0V$  (for half positive cycle of WL) at this time SA sense the difference between BTL and BTL<sub>BAR</sub> and the stored data has been perceived as because PM16, PM17, PM18 are in active mode BTL<sub>BAR</sub> is started discharging. When the voltage of BTL<sub>BAR</sub> goes to  $V_b+|V_{V_b}|$ , PM13 goes into the sub-threshold region. Whereas BTL= $V_{DD}$  charges the output nodes  $SA_5$  to  $V_{DD}$ , stored data can be sensed through  $V_3$ . Figure: 15 shows single Bit 6T-SRAM CTDSA architecture chip design.

Figure: 15 Single Bit 6T- SRAM CTDSA Architecture Chip Design.

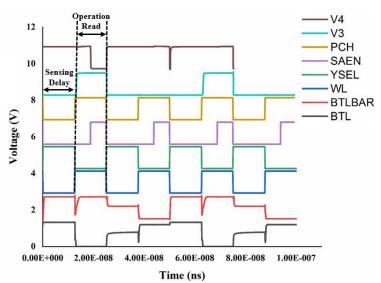

Figure:16 shows the output waveform of CTDSA,  $Y_{SEL}$ =0, precharge circuits keeps high to precharge the bit-lines (i.e.,  $P_{ch}$ = $V_{DD}$ ), data on the bit-lines are passed from 6T-SRAM to sense amplifier, WL of 6T-SRAM cell keeps high (i.e., WL= $V_{DD}$ ) for reading operation, i.e., access transistors are turned ON, BTL= 0V and BTL<sub>BAR</sub>= $V_{DD}$ , i.e., a voltage difference is  $V_{DD}$  at the output,  $SA_{EN}$ =0V (for half positive cycle of WL) at this time sense amplifier sense the difference between BTL and BTL<sub>BAR</sub> and the stored data has been sensed by the sense amplifier and stored is shown at  $V_4$ , i.e., logic "1" is stored at the memory and hence sense by SA.

<u>www.iaset.us</u> editor@iaset.us

Figure 16: Shows Single Bit 6T-SRAM CTDSA Architecture Output Waveform.

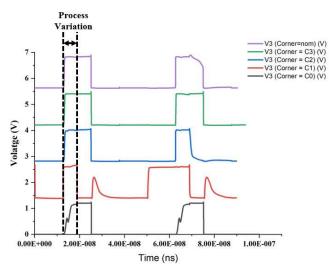

Figure: 17 shows the Process Corner Simulation of Output V<sub>3</sub> of Sense Amplifier.

**Figure: 17 Process Corner Variations**

Five corners are shown in the figure as follows;

- a) V3 (Corner=C3) significant that both  $N_{mos}$  and  $P_{mos}$  are slow (SS),

- b) V3(Corner=C2) significant that both  $N_{\text{mos}}$  and  $P_{\text{mos}}$  are fast (FF),

- c) V3(Corner=C1) significant that  $N_{mos}$  is fast and  $P_{mos}$  is slow (FS),

- d) V3(Corner=C0) significant that  $N_{mos}$  and is slow  $P_{mos}$  is Fast (SF),

- e) V3(Corner=nom) significant that both  $N_{\text{mos}}$  and  $P_{\text{mos}}$  have typical values (NN).

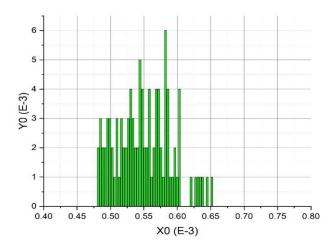

Figure: 18 Monte Carlo Simulations.

In this paper, there are tradeoffs between power consumption and area. Due to this region, different type of sense amplifiers has been analyzed to use the lowest power consumption, and different techniques are applied over 6T-SRAM and SA. Figure: 18 shows the Monte Carlo simulations of VTH\_SAEN, on which the sense amplifier of a single-bit cache memory sense amplifier depends.

Table: 1 displays the various cache memory design parameters for a single-bit architecture. Different sense amplifiers are analyzed concerning their sensing delay parameter, and there is also an increase in area and a decrease in power. The conclusion is that the Single Bit 6T-SRAMC VDSA Architecture consumes 13.16  $\mu$ Wof power with 30 transistors in the design, giving low power consumption and less area.

Table: 1 Single Bit 6T- SRAM SA ArchitectureAnalysis of Different Parameters

| •             |          |    |

|---------------|----------|----|

| Architectures | CP       | NT |

| SB6T-SRAMVA   | 13.16 μW | 30 |

| SB6T-SRAMCA   | 16.44 μW | 33 |

| SB6T-SRAMCTA  | 44.63 μW | 37 |

Total Power = Dynamic Power + Static Power (i.e., Total Power ≈ Dynamic Power)

If a reduction in static power does not much affect total power due to this reason, the main focus is on total power consumption. Due to this reason, power reduction techniques are applied instead of leakage power reduction techniques and also analyzed that there is no change in input and output of the design.

Table: 2 Single Bit6T-SRAM VDSA ArchitectureAnalysis of Different Parameters on Applying Techniques of Power Reduction over VDSA

| S.No. | Architecture | SB6T-SI  | RAMVA |

|-------|--------------|----------|-------|

|       | Techniques   | CP       | NT    |

| 1.    | PRSTT        | 12.87 μW | 32    |

| 2.    | PRFST        | 13.03 μW | 32    |

| 3.    | PRSST        | 13.03 μW | 33    |

| 4.    | PRDST        | 12.88 μW | 34    |

\*Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAM

VDSA Architecture (SB6T-SRAMVA), Consumption of Power (CP), Number of Transistor (NT)

Table: 2 describes those techniques of power reduction applied over VDSA in Single Bit 6T-SRAM VDSA Architecture. There is reduced power consumption, which increases our circuit's working capacity. The conclusion arises that Single Bit 6T-SRAM VDSA with power reduction sleep transistor technique in Architecture consumes 12.87  $\mu$ W of power with 32 transistors.

Table: 3 Single Bit6T-SRAM CDSA Architecture Analysis of Different Parameters on Applying Techniques of Power Reduction over CDSA

| S.No. | Architecture | SB6T-SR  | AMCA |

|-------|--------------|----------|------|

|       | Techniques   | CP       | NT   |

| 1.    | PRSTT        | 14.28 μW | 35   |

| 2.    | PRFST        | 14.17 μW | 35   |

| 3.    | PRSST        | 14.82 μW | 36   |

| 4.    | PRDST        | 14.52 μW | 37   |

<sup>\*</sup>Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAMCDSA Architecture (SB6T-SRAMCA), Consumption of Power (CP), Number of Transistor (NT)

Table: 3 describes that applying power reduction techniques over CDSA in Single Bit 6T-SRAM CDSA Architectureto reduce consumption of power and concludes that single bit 6T-SRAM CDSA with power reduction forced stack technique in architecture consumes 14.17 μW of power with 35 transistors in design which increases area, i.e., ↓power consumption and ↑area.

Table 4 describes applying power reduction techniques over CTDSA in a Single Bit 6T-SRAM CTDSA Architecture to reduce power consumptionand concludes that single bit 6T-SRAM CTDSA with power reduction forced stack technique in architecture consumes 20.07 μW of power with 40 transistors in design.

Table 4: Single Bit6T-SRAM CTDSA Architecture Analysis of Different Parameters on Applying Techniques of Power Reduction over CTDSA

| S.No.  | Architecture | SB6T-SRAMCTA |    |  |

|--------|--------------|--------------|----|--|

| 5.110. | Techniques   | CP           | NT |  |

| 1.     | PRSTT        | 20.74 μW     | 39 |  |

| 2.     | PRFST        | 20.74 μW     | 39 |  |

| 3.     | PRSST        | 20.07 μW     | 40 |  |

| 4.     | PRDST        | 21.74 μW     | 41 |  |

<sup>\*</sup>Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-

SRAMCTDSA Architecture (SB6T-SRAMCTA), Consumption of Power (CP), Number of Transistor (NT)

| Table 5: Single Bit6T-SRAMVDSAArchitecture Analysis of Different Parameters on Applying Techniques of Power Reduction over 6T-SRAM |             |          |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|----|--|--|--|

|                                                                                                                                    | SR6T-SRAMVA |          |    |  |  |  |

| S.No.                                                                                                                              | TA6T-SRAMA  | СР       | NT |  |  |  |

| 1.                                                                                                                                 | PRSTT       | 9.39 μW  | 32 |  |  |  |

| 2.                                                                                                                                 | PRFST       | 9.31 μW  | 32 |  |  |  |

| 3.                                                                                                                                 | PRSST       | 11.50 μW | 33 |  |  |  |

| 4.                                                                                                                                 | PRDST       | 11.11 μW | 34 |  |  |  |

<sup>\*</sup> Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAM VDSA Architecture (SB6T-SRAMVA), Consumption of Power (CP), Number of Transistor (NT)

Table: 5 describes applying power reduction techniques over 6T-SRAM in Single Bit 6T-SRAM VDSA Architectureto reduce power consumptionand concludes that single bit 6T-SRAM VDSA with power reduction forced

stack technique in architecture consumes 9.31 µW of power with 32 transistors in design.

Table 6: Single Bit6T-SRAM CDSA Architecture Analysis of Different Parameters on Applying Techniques of Power Reduction over 6T-SRAM

| S.No.  | TA6T-SRAMA    | SB6T-SRAMCA |    |

|--------|---------------|-------------|----|

| 5.110. | 17101-5101111 | CP          | NT |

| 1.     | PRSTT         | 13.62 μW    | 35 |

| 2.     | PRFST         | 12.68 μW    | 35 |

| 3.     | PRSST         | 14.14 μW    | 36 |

| 4.     | PRDST         | 13.88 μW    | 37 |

<sup>\*</sup>Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAMCDSA Architecture (SB6T-SRAMCA), Consumption of Power (CP), Number of Transistor (NT)

Table 6 describes applying power reduction techniques over 6T-SRAM in Single Bit 6T-SRAM CDSA Architecture to reduce power consumptionand concludes that single bit 6T-SRAM CDSA with power reduction forced stack technique in architecture to consume 12.68 μW of power with 35 transistors in design.

Table 7 describes applying power reduction techniques over 6T-SRAM in Single Bit 6T-SRAM CTDSA Architecture to reduce power consumption and concludes that single bit 6T-SRAM CTDSA with power reduction dual sleep technique in architecture consumes 13.88 μW of power with 41 transistors in design.

Table: 7 Single Bit6T6T-SRAM CTDSA Architecture Analysis of Different Parameters on Applying Techniques of Power Reduction over 6T-SRA

| S.No. | TA6T-SRAMA | SB6T-SRAMCTA |    |  |

|-------|------------|--------------|----|--|

|       |            | CP           | NT |  |

| 1.    | PRSTT      | 14.14 μW     | 39 |  |

| 2.    | PRFST      | 41.66µW      | 39 |  |

| 3.    | PRSST      | 43.64 μW     | 40 |  |

| 4.    | PRDST      | 13.88 μW     | 41 |  |

<sup>\*</sup> Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAMCTDSA Architecture (SB6T-SRAMCTA), Consumption of Power (CP), Number of Transistor (NT)

Table: 8 describes applying power reduction techniques over 6T-SRAM and VDSA in Single Bit 6T-SRAM VDSA Architecture reduce power consumption and concludes that single Bit 6T-SRAM with power reduction sleep transistor technique VDSA with power reduction sleep transistor technique in architecture consumes  $8.988~\mu W$  of power with 34 transistors in design.

Table 8 Single Bit6T-SRAM VDSA Architecture Different Parameters on Applying Techniques of Power Reduction over 6T-SRAM and VDSA

| S.NO. | TA6T-SRAMA | SB6T-SRAMVA |    |  |

|-------|------------|-------------|----|--|

|       |            | CP          | NT |  |

| 1.    | PRSTT      | 8.988 μW    | 34 |  |

| 2.    | PRFST      | 9.332μW     | 34 |  |

| 3.    | PRSST      | 9.331 μW    | 36 |  |

| 4.    | PRDST      | 10.71 μW    | 38 |  |

\*Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-

SRAMCTDSA Architecture (SB6T-SRAMVA), Consumption of Power (CP), Number of Transistor (NT)

Table: 9 describes applying power reduction techniques over 6T-SRAM and CDSA in Single Bit 6T-SRAM CDSA Architectureto reduce power consumption and concludes that single Bit 6T-SRAM with power reduction forced stack technique CDSA with power reduction forced stack technique in architecture consumes  $12.52~\mu W$  of power with 37 transistors in design.

Table: 9 Single Bit6T-SRAM CDSA Architecture Different Parameters on Applying Techniques of Power Reduction over 6T-SRAM and CDSA

| S.NO. | TA6T-SRAMA | SB6T-SRAMCA |    |  |

|-------|------------|-------------|----|--|

|       |            | СР          | NT |  |

| 1.    | PRSTT      | 12.99 μW    | 37 |  |

| 2.    | PRFST      | 12.52μW     | 37 |  |

| 3.    | PRSST      | 14.03µW     | 39 |  |

| 4.    | PRDST      | 13.52uW     | 41 |  |

\*Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-SRAMCTDSA Architecture (SB6T-SRAMCA), Consumption of Power (CP), Number of Transistor (NT)

Table: 10 explains how to apply power reduction techniques to 6T-SRAM and CTDSA in Single Bit 6T-SRAM CDSA Architecture to reduce power consumption. It concludes that Single Bit 6T-SRAM with Power Reduction Forced Stack Technique CDSA with Power Reduction Forced Stack Technique in Architecture consumes18.15 μWof Power with 41 Transistors in Design.

Table 10: Single Bit6T-SRAM CTDSA Architecture Different Parameters on Applying Techniques of Power Reduction over 6T-SRAM and CTDSA

| S.NO. | TA6T-SRAMA | SB6T-SRAMCTA |    |  |

|-------|------------|--------------|----|--|

|       |            | CP           | NT |  |

| 1.    | PRSTT      | 18.15 μW     | 41 |  |

| 2.    | PRFST      | 18.12 μW     | 41 |  |

| 3.    | PRSST      | 19.20 μW     | 43 |  |

| 4.    | PRDST      | 18.85 μW     | 45 |  |

<sup>\*</sup>Techniques Applied over 6T-SRAM in Architecture (TA6T-SRAMA), Single Bit 6T-

SRAMCTDSA Architecture (SB6T-SRAMCTA), Consumption of Power (CP), Number of Transistor (NT)

## 5. CONCLUSIONS

Cache Memory Design for Single-Bit Architecture has been implemented with VDSA, CDSA, and CTDSA and compared in the proposed work. Architecture composed of Circuit of Write Driver, 6T-SRAM and SA's and different architecture has been analyzed such as Single Bit 6T-SRAM VDSA Architecture, Single Bit 6T-SRAM CDSA Architecture and Single Bit 6T-SRAM CTDSA Architecture in terms of consumption of power and number of transistors. Apart from optimizing power consumption, power reduction techniques have been applied to different architecture blocks. The result depicted that Single Bit 6T-SRAM with power reduction sleep transistor technique VDSA with power reduction sleep transistor technique in architecture consumesthe lowest power but area increases. All simulations have been done in 45nm CMOS technology on the cadence virtuoso tool. Furthermore, Process corner simulation and Monte Carlo simulation also have been done to check the robustness of the proposed design, and there is no variation of more than three percent. In the future, this work can be extended as an array.

## **REFERENCES**

- 1. Jain, F., et al. "multi-Bit6T-SRAMs, Registers, and Logic Using Quantum Well Channel SWS-FETs for Low-Power, High-Speed Computing." International Journal of High-Speed Electronics and Systems 28.03n04 (2019).

- 2. Jain, Faquir, et al. "Multi-State 2-Bit CMOS Logic Using n-and p-Quantum Well Channel Spatial Wavefunction Switched (SWS) FETs." International Journal of High-Speed Electronics and Systems 27.03n04 (2018).

- Saman, Bander, et al. "Spatial Wavefunction Switched (SWS) FET 6T-SRAM Circuits and Simulation." International Journal of High-Speed Electronics and Systems 26.03 (2017).

- Global Consumer Electronics Market to Reach US\$ 2.9 Trillion by 2020 Persistence Market Research". PR Newswire. Persistence Market Research. January 3, 2017. Retrieved October 11, 2019.

- 5. "1960 Metal Oxide Semiconductor (MOS) Transistor Demonstrated". The Silicon Engine. Computer History Museum.

- 6. "Who Invented the Transistor?". Computer History Museum. December 4, 2013. Retrieved July 20, 2019.

- 7. "13 Sextillion & Counting: The Long & Winding Road to the Most Frequently Manufactured Human Artifact in History". Computer History Museum. April 2, 2018. Retrieved July 28, 2019.

- 8. Y. He, J. Zhang, X. Wu, X. Si, S. Zhen, and B. Zhang, "A Half-Select Disturb-Free 11T 6T-SRAM Cell With Built-In Write/Read-Assist Scheme for Ultralow-Voltage Operations," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 10, pp. 2344-2353, Oct. 2019.

- 9. R. Fragasse et al., "Analysis of 6T-SRAM Enhancements Through Sense Amplifier Capacitive Offset Correction and Replica Self-Timing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 6, pp. 2037-2050, June 2019.

- 10. S. Gupta, K. Gupta, B. H. Calhoun, and N. Pandey, "Low-Power Near-Threshold 10T 6T-SRAM Bit Cells With Enhanced Data-Independent Read Port Leakage for Array Augmentation in 32-nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 3, pp. 978-988, March 2019.

- 11. H. Dounavi, Y. Sfikas, and Y. Tsiatouhas, "Periodic Aging Monitoring in 6T-SRAM Sense Amplifiers," 2018 IEEE 24th International Symposium on On-Line Testing And Robust System Design (IOLTS), Platjad'Aro, 2018, pp. 12-16.

- 12. S. Ahmad, B. Iqbal, N. Alam, and M. Hasan, "Low Leakage Fully Half-Select-Free Robust 6T-SRAM Cells With BTI Reliability Analysis," in IEEE Transactions on Device and Materials Reliability, vol. 18, no. 3, pp. 337-349, Sept. 2018, B. N. K. Reddy, K. Sarangam, T. Veeraiah, and R. Cheruku, "6T-SRAM cell with better read and write stability with Minimum area," TENCON 2019 2019 IEEE Region 10 Conference (TENCON), Kochi, India, 2019, pp. 2164-2167.

- A. Surkar and V. Agarwal, "Delay and Power Analysis of Current and Voltage Sense Amplifiers for 6T-SRAM at 180nm Technology," 2019 3rd International Conference on Electronics, Communication, and Aerospace Technology (ICECA), Coimbatore, India, 2019, pp. 1371-1376.

13. Kobayashi, Masaharu, Nozomu Ueyama, and Toshiro Hiramoto. "A non-volatile 6T-SRAM integrated with ferroelectric HfO<sub>2</sub>capacitor for normally-off and ultralow-power IoT application." In VLSI Technology, 2017 Symposium on, pp. T156-T157. IEEE, 2017.

- 14. Pandey, Sunil, Shivendra Yadav, Kaushal Nigam, Dheeraj Sharma, and P. N. Kondekar. "Realization of Junctionless TFET-Based Power Efficient 6T 6T-SRAM Memory Cell for the Internet of Things Applications." In Proceedings of First International Conference on Smart System, Innovations and Computing, pp. 515-523. Springer, Singapore, 2018.

- 15. Jeong, Hanwool, Tae Woo Oh, Seung Chul Song, and Seong-Ook Jung. "Sense-Amplifier-Based Flip-Flop with Transition Completion Detection for Low-Voltage Operation." IEEE Transactions on Very Large-Scale Integration (VLSI) Systems (2018).

- 16. K Sridhara, G S Biradar, Raju Yanamshetti, "Subthreshold leakage power reduction in VLSI circuits: A survey," Communication and Signal Processing (ICCSP) 2016 International Conference on, pp. 1120-1124, 2016.

- 17. Afshin Abdollahi, Farzan Fallah, Massoud Pedram, "A Robust Power Gating Structure and Power Mode Transition Strategy for MTCMOS Design," Very Large-Scale Integration (VLSI) Systems IEEE Transactions on, vol. 15, pp. 80-89, 2007.

- 18. Rajendra Prasad S, BK Madhavi, K Lal Kishore, "design of 32nm Forced Stack CNTFET 6T-SRAM Cell for Leakage Power Reduction", IEEE Conference on Computing, Electronics, and Electrical Technologies, pp. 629-633, 2012.

- A. Sathanur, A. Pullini, L. Benini, A. Macii, E. Macii, M. Poncino, "A ScalaBTLe Algorithmic Framework for Row-Based Power-Gating," Design Automation and Test in Europe 2008. DATE '08, pp. 379-384, 2008.

- 19. J. K. Mishra, H. Srivastava, P. K. Misra, and M. Goswami, "A 40nm Low Power High StaBTLe6T-SRAM Cell Using Separate Read Port and Sleep Transistor Methodology," 2018 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Hyderabad, India, 2018, pp. 1-5.

- 20. Tarunnum Sultana, S.Jagadesh, M.Naveen Kumar, "A Novel Dual-Stack Sleep Technique for Reactivation Noise Suppression in MTCMOS Circuits," IOSR Journal of VLSI and Signal Processing, Vol.-3, pp.32-37, 2013.

- 21. K.Gnana Deepika, K.Mariya Priyadarshini, K. David Solomon Raj. "Sleepy Keeper Approach for Power Performance Tuning in VLSI Design." International Journal of Electronics and Communication Engineering, Volume 6, Number 1(2013), pp.17-28.

- 22. Reeya Agrawal, V.K. Tomar "Implementation and analysis of low power reduction techniques in sense amplifier" Proceedings of the 2nd International Conference on Electronics, Communication, and Aerospace Technology (ICEC 2018), pp:447-452.

- 23. Chakka Sri Harsha Kaushik, Rajiv Reddy Vanjarlapati, Varada Murali Krishna, Tadavarthi Gautam, V Elamaran, "VLSI design of low power 6T-SRAM architectures for FPGAs", Green Computing Communication and Electrical Engineering (ICGCCEE) 2014 International Conference on, pp. 1-4, 2014.

- 24. Richa Choudhary, SrinivasaPadhy, NirmalKumar Rout, "Enhanced Robust Architecture of Single Bit 6T-SRAM Cell using Drowsy Cache and Super cut-off CMOS Concept", International Journal of Industrial Electronics and Electrical Engineering, Volume-3, PP.63-68, July 2011.

- 25. Jesal P. Gajjar, Aesha S. Zala, Sandeep K. Aggarwal, "Design and Analysis of 32-bit6T-SRAM architecture in 90nm CMOS Technology" Volume: 03, Issue: 04, Apr-2016, pp:2729-2733.

- 26. Reeya Agrawal, V. K. Tomar. "Analysis of Cache (6T-SRAM) Memory for Core I ™ 7 Processor", 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018.

- 27. Reeya Agrawal, V.K. Tomar "Implementation and analysis of Differential-Type and Latch-type Sense Amplifier Circuits with IJOW Power Reduction Techniques in sub-90-nm"Proceedings of International Conference on Frontiers in Engineering, Applied Sciences and Technology, (FEAST' 18), April 2018,pp:115-120.

- 28. Kundan Vanama, Rithwik Gunnuthula, Govind Prasad, "Design of low power stable 6T-SRAM cell", Circuit Power and Computing Technologies (ICCPCT) 2014 International Conference on, pp. 1263-1267, 2014.

- 29. Shikha Saun, Hemant Kumar, "Design and performance analysis of 6T 6T-SRAM cell on different CMOS technologies with stability characterization", OP Conf. Series: Materials Science and Engineering 561 2019.

- 30. 32. Bazzi, H., Harb, A., Aziza, H. et al.RRAM-based non-volatile 6T-SRAM cell architectures for ultra-low-power applications. Analog Integr Circ Sig Process (2020).

- 31. Ishibashi, K., & Osada, K. (2011). Low power and reliable 6T-SRAM memory cell and array design. Berlin: Springer.

- 32. Guin, U., et al. (2019). Detecting recycled SoCs by exploiting aging-induced biases in memory cells. In IEEE international symposium on hardware-oriented security and trust.

- 33. Baker Mohammad, Percy Dadabhoy, Ken Lin, Paul Bassett. "Comparative study of current mode and voltage mode sense amplifier used for 28nm 6T-SRAM." 24th International Conference on Microelectronic, March 7, 2013.

- 34. Yong-peng Tao, Wei-ping Hu, "Design of Sense Amplifier in the High-Speed 6T-SRAM", International Conference on Cyber-EnaBTLed Distributed Computing and Knowledge Discovery, pp. 384-387, 2015.

- 35. Shalini, Anand Kumar. "DESIGN OF HIGH SPEED AND LOW POWER SENSE AMPLIFIER FOR 6T-SRAM APPLICATIONS." International Journal of Scientific & Engineering Research, Volume 4, Issue 7, July-2013.

- 36. Manoj Sinha, Steven Hsu, Atila Alvandpour, Wayne Burleson, Ram Krishnamurthy, Shekhar Borhr. "High-Performance and Low-Voltage Sense-Amplifier Techniques for sub-90nm 6T-SRAM"SOC Conference, 2003. Proceedings. IEEE International [Systems-on-Chip]

- 37. Ravi Dutt, Abhijeet. "High-Speed Current Mode Sense Amplifier for 6T-SRAM Applications." IOSR Journal of Engineering, Vol. 2, pp: 1124-1127, 2012

- 38. L. Heller; D. Spampinato; Ying Yao. "High-sensitivity charge-transfer sense amplifier" Solid-State Circuits Conference. Digest of Technical Papers. 1975 IEEE International.

<u>www.iaset.us</u> editor@iaset.us